Курсовая работа

Узел приемопередатчика с блоком преобразователя сигналов ТТЛ

Содержание

|

Введение…………………………………………………………………………… |

3 |

|

1 Исходные данные …………………………………………………………………. |

4 |

|

2 Модуль УМПК-80/МИ1…………………………...…………...………………. |

5 |

|

2.1 Назначение…................................................................................................. |

5 |

|

2.2 Краткое описание микросхем, входящих в модуль……………………… |

5 |

|

2.3 Структурная схема модуля …………………..………………..................... |

7 |

|

2.4 Описание состава модуля…………………………………………………. |

8 |

|

2.5 Функциональная схема модуля …………….…………………………….. |

9 |

|

2.6 Описание работы модуля……………......................................................... |

10 |

|

3 Узел приемопередатчика с блоком преобразователя сигналов ТТЛ модуля УМПК-80/МИ1………………………………...…………………………………. |

11 |

|

3.1 Назначение………………………………………………………………… |

11 |

|

3.2 Описание микросхем входящих в узел…………………………………... |

11 |

|

3.3 Функциональная схема узла………………………..…………………….. |

18 |

|

3.4 Описание работы узла……………………………………………………………. |

18 |

|

3.5 Описание принципиальной электрической схемы узла………………… |

18 |

4 Расчет временных задержек в схеме функционального узла………….….… |

19 |

|

5 Расчет мощности, потребляемой узлом от источника питания ……………. |

20 |

|

Вывод…………….……………………………………………………………… |

21 |

|

Список использованных источников ……………………….………. …………. |

22 |

|

Приложение А. Перечень элементов……………………………………………. |

23 |

Введение

Микропроцессоры, построенные на одной БИС, содержат в своем составе устройство управление, реализующее фиксированную для конкретной микросхемы систему команд, и имеют ограниченное количество внешних магистралей.

Другую значительную группу МПК представляют схемы, в которых устройство управления и операционный блок реализуется на отдельных БИС и разработчик имеет возможность формировать необходимую систему команд. Операционный блок в таких системах чаще всего выполняется на секционируемых БИС, позволяющих увеличивать разрядность обрабатываемых слов.

К третьей группе МПК можно отнести схемы, в которых устройство управления реализованного на основе программируемых логических матриц, содержащих информацию, обеспечивающую выполнение записанной в них системы команд.

Учебный микропроцессорный комплекс УМПК-80 предназначен для изучения специфики построения микро-ЭВМ на базе МП БИС с фиксированным набором команд, исследования работы и методов программирования БИС, входящих в МПК серии К580, а также для изучения особенностей разработки и отладки программного схемотехнического обеспечения микропроцессорных систем на их основе, включая построение схем универсальных и специализированных интерфейсов с использованием ИБИС и БИС контроллеров серии К580.

Особенностью учебного микропроцессорного комплекса УМПК-80, обусловленной легкостью изменения структуры системы и большим количеством модулей, реализующих различные функции, является возможность построения устройств различной сложности, от простейшей одноплатной микро-ЭВМ со встроенной клавиатурой и дисплеем до измерительно-вычислительного комплекса и персонального компьютера с развитой сетью периферийных устройств.

Применение программной модели дает значительную экономию времени и сил, за счет более удобной отладки и набора программы.

1 Исходные данные

Вариант индивидуального задания – 10.

Модуль – УМПК-80/МИ1.

Функциональный узел – узел приемопередатчика с блоком преобразователя сигналов ТТЛ.

2 Модуль УМПК-80/МИ1

Модуль УМПК-80/МИ1 учебного микропроцессорного комплекса (УМПК) УМПК-80 на базе микропроцессорной БИС КР580ВМ80А, входящего в состав лаборатории изучения микропроцессорных систем «Пирамида», представляет собой функционально завершенный узел, позволяющий создавать основные используемые сигналы, индицировать принимаемую/передаваемую и контрольную информацию, прослеживать прохождение и изменение информации в процессе работы модуля.

2.1 Назначение

Модуль УМПК-80/МИ1 предназначен для изучения методов построения контроллеров последовательного интерфейса, способов обмена информацией в последовательном коде, а так же для изучения БИС универсального синхронно асинхронного приемопередатчика (УСАПТ) КР580ВВ51А и БИС программируемого интервального таймера (ПИТ) КР580ВИ53 во всех режимах работы. Модуль УМПК-80/МИ1 ориентирован на использование в микропроцессорных системах (МПС) на базе микропроцессорного комплекта (МПК) серии КР580.

2.2 Краткое описание микросхем, входящих в модуль

Таблица 1 – Микросхемы модуля УМПК-80/МИ1

|

Марка |

Название |

Назначение |

Режим работы |

|

К555ТЛ2 |

Шесть триггеров Шмитта – инверторов |

Используется для очистки сигнала от помех и калибровки цифрового импульса. |

|

|

К555ЛЛ1 |

Четыре логических элемента 2ИЛИ |

Выполняет логическую функцию «ИЛИ» |

|

|

КР556РТ4А |

Программируемое постоянное запоминающее устройство |

Выполняет функцию запоминающего устройства емкость 1024 бит |

- режим программирования - режим считывания информации |

Продолжение таблицы 1

|

Марка |

Название |

Назначение |

Режим работы |

|

КР580ВА86 |

Двунаправленный 8-разрядный шинный формирователь |

Осуществляет обмен данными между микропроцессором и системной шиной. |

- только для приёма информации; - только для выдачи информации; - двунаправленная передача информации |

|

К555ТМ2 |

Два независимых D-триггера |

Преобразует входную информацию в комбинацию сигналов |

|

|

К555КП11 |

Четырехразрядный селектор 2 – 1 без инверсии |

Выполняет мультиплексирование (кодирование) сигналов |

|

|

К561ПУ4 |

Шесть преобразователей сигналов ТТЛ уровня |

|

|

|

КР580ВВ51А |

Программируемый последовательный интерфейс |

Универсальный синхронно-асинхронный приемо-передатчик |

|

|

К293ЛП1Б |

Оптоэлектронный переключатель инвертор |

|

|

|

КР580ВИ53 |

Трехканальный программируемый таймер |

Предназначен для организации работы микропроцессорных систем в режиме реального времени и позволяет формировать сигналы с различными временными и частотными характеристиками. |

- режим программирования - режим считывания информации |

2.3 Структурная схема модуля

Структурная схема модуля УМПК–80/МИ1, представлена на рисунке 1.

Рисунок 1 – Структурная схема модуля УМПК–80/МИ1

2.4 Описание состава модуля

Ниже приводится поблочное описание устройства модуля по структурной схеме.

На плате модуля УМПК-80/МИ1 размещены:

- Блок программируемого интервального таймера – БПИТ: МП БИС КР580ВИ53, шесть триггеров Шмитта-инверторов К555ТЛ2, четыре логических элемента 2ИЛИ К555ЛЛ1, два D-триггера К555ТМ2;

- Блок преобразователя сигналов ТТЛ – БТТЛ: четырех разрядный селектор 2-1 без инверсии, преобразователь уровня К561ПУ4;

- Блок формирования сигналов – БФС: шесть триггеров Шмитта-инверторов К555ТЛ2;

- Блок приемо-передатчика – БПП: шесть преобразователей уровня К561ПУ4;

- Блок буферирования и дешифрации – ББД: шесть триггеров Шмитта-инверторов К555ТЛ2, четыре логических элемента 2ИЛИ К555ЛЛ1, двунаправленный 8-разрядный шинный формирователь КР580ВА86, программируемое постоянное запоминающие устройство КР556РТ4А;

- Блок управления режимом работы – БУРР: четырех разрядный селектор 2-1 без инверсии с тремя устойчивыми состояниями К555КП11.

- Магистраль адреса – МА;

- Магистраль данных – МД;

- Магистраль управления – МУ.

|

2.5 Функциональная схема модуля

Функциональная схема модуля УМПК–80/МИ1, представлена на рисунке 2. |

|

СА – сигнал адреса СД – сигнал данных СУ – сигнал управления УСАПП – универсальный синхронно-асинхронный приемо-передатчик ПИТ – программируемый интервальный таймер

Рисунок 2 – Функциональная схема модуля УМПК–80/МИ1 |

2.6 Описание работы модуля

Функционально модуль состоит из блока программируемого интервального таймера, блока преобразователя сигналов ТТЛ, блока формирования сигналов, блока приемо-передатчика, блока буферирования и дешифрации, блока управления режимом работы и трех магистралей: магистрали адреса, магистрали данных и магистрали управления.

Обмен информацией между МП БИС КР580ВВ51А и внешними устройствами организуется с помощью трех магистралей: магистраль адреса, магистраль данных, магистраль управления. Магистраль адресов является однонаправленной магистралью, выдача адресов на которую осуществляется лишь МП БИС КР580ВВ51А. Малая нагрузочная способность магистрали адреса требует применения буфера, роль которого выполняет микросхема КР580ВА86. По магистрали данных организуется двунаправленный обмен данными между МП БИС КР580ВВ51А и памятью или внешним устройством. Все сигналы управления в электронной системе согласованы с блоком синхронизации, выполненного на БИС КР580ВИ53, которая является центральным элементом блока и реализует необходимые для исследования функции формирования сигнала с программируемыми временными параметрами. Эти сигналы задают начало и последовательность срабатывания различных устройств системы.

Для программирования частоты передачи/приема необходимо вписать по адресу 9BH регистра управления ПИТ байт определения режима работы и по адресу 9AH нагрузить счетчик второго канала. Тактовые импульсы с ПИТ поступают на УСАПП при разомкнутом переключателе SA 3.2 и замкнутом переключателе SA 2.2.

Возможно два режима работы модуля УМПК-80/МИ1: автоматический и ручной.

Автоматический режим модуля УМПК-80/МИ1 осуществляет переключатель SA 2.1. Сигналы синхронизации приема/передачи формируются блоком ПИТ, принимаемые последовательные данные поступают с блока преобразования стандарта «20 mA токовая петля». Таким образом, в этом режиме можно организовать последовательный 20 mA канал обмена для микро-ЭВМ с внешним устройством. При разомкнутом переключателе SA 2.1 мультиплексор К555КП11 коммутирует на вход сигналы, формируемые с SA 1.1 и SA 1.2.

Ручной режим модуля, задаваемый с помощью переключателей SA 1, SA 4, схемы антидребезга и схемы формирования сигнала E 2.4, позволяет проследить работу УСАПП по шагам.

3 Узел приемопередатчика с преобразователем сигналов ТТЛ модуля УМПК-80/МИ1

3.1 Назначение

Узел преобразования сигнала ТТЛ преобразует сигнал передатчика УСАПП ТТЛ-уровня в стандартные 20 мА токовые петли и выполняет обратное преобразование в сигнал приемника УСАПП ТТЛ-уровня.

3.2 Описание микросхем входящих в узел

Узел приемо-передатчика – предназначенный для организации обмена информацией в последовательном коде, включает:

– БИС УСАПП КР580ВВ51А – универсальный синхронно-асинхронный приемопередатчик;

– источники формирования тока для светодиодных индикаторов, индикации выходных сигналов TXD, RXRDY, TXRDY, TXEND, , , УСАПП соответственно, и индикаторов входных сигналов RXD и (HL1 и HL2 соответственно).

Блок преобразователя сигналов ТТЛ, преобразующего сигнал передатчика УСАПП ТТЛ-уровня в стандарте «20 мА токовой петли», и выполняет обратное преобразование в сигнал приемника УСАПП ТТЛ-уровня, состоит из:

- схемы формирования тока 20 мА;

- схемы передающей части;

- схемы принимающей части.

Работа блока определяется функционированием БИС УСАПП.

Рассмотрим более подробно микросхему К561ПУ4.

Микросхема К561ПУ4 представляет собой шесть преобразователей уровня. Применяется для согласования КМОП- и ТТЛ-схем, а также низкопороговых и высокопороговых КМОП-схем.

Полное условно-графическое обозначение микросхемы К561ПУ4 представлено на рисунке 3.1.

Рисунок 3.1 – Условно-графическое обозначение К561ПУ4

Описание выводов и основные параметры микросхемы К561ПУ4 представлены в таблицах 3.1 и 3.2 соответственно.

Таблица 3.1 – Назначение выводов микросхемы К561ПУ4

|

Номер вывода |

Обозначение |

Назначение вывода |

|

1 |

VCC |

напряжение питания |

|

2, 4, 6, 10, 12, 15 |

O0, O1, O2, O3, O4, O5 |

выход |

|

3, 5, 7, 9, 11, 14 |

I0, I1, I2, I3, I4, I5 |

вход |

|

8 |

GND |

общий |

|

13, 16 |

NC |

свободный |

Таблица 3.2 – Основные электрические параметры К561ПУ4

|

Параметры |

Величина |

|

Напряжение питания |

3…15 В |

|

Выходное напряжение высокого уровня |

|

|

При Uп=5 В |

≥4,99В |

|

Продолжение Таблицы 3.2 |

|

|

При Uп=10 В |

≥9,99В |

|

Выходное напряжение низкого уровня |

≤0,01 В |

|

Максимальное выходное напряжение низкого уровня |

|

|

При Uп=5 В |

≤0,95 В |

|

При Uп=10 В |

≤2,9 В |

|

Минимальное выходное напряжение низкого уровня |

|

|

При Uп=5 В |

≥3,6 В |

|

При Uп=10 В |

≥7,2 В |

|

Входной ток низкого (высокого) уровня при Uп=10 В |

≤0,2 мкА |

|

Выходной ток низкого уровня |

|

|

При Uп=5 В |

≥3 мА |

|

При Uп=10 В |

≥8 мА |

|

Выходной ток высокого уровня |

≥1,25 мА |

|

Время задержки распространения при включении |

|

|

При Uп=5 В |

≤240 нс |

|

При Uп=10 В |

≤110 нс |

|

Время задержки распространения при выключении |

|

|

При Uп=5 В |

≤280 нс |

|

При Uп=10 В |

≤140 нс |

Рассмотрим более подробно микросхему КР580ВВ51А.

Микросхема КР580ВВ51А представляет собой программируемый последовательный интерфейс (универсальный синхронно-асинхронный приемо-передатчик (УСАПП)).

УСАПП предназначен для аппаратной реализации последовательного протокола обмена между микропроцессором КР580ВМ80А (КМ1810ВМ86) или другим устройством, способным запрограммировать данную микросхему на требуемый режим работы, и каналами последовательной передачи дискретной информации.

Микросхема УСАПП преобразует параллельный код, получаемый от центрального процессора, в последовательный поток символов со служебными битами и выдает этот поток в последовательный канал связи с различной скоростью, а также выполняет обратное преобразование: последовательный поток символов – в параллельное 8-разрядное слово. Передаваемая и принимаемая информация при необходимости может контролироваться на четность (нечетность).

Полное условно-графическое обозначение микросхемы К561ПУ4 представлено на рисунке 3.2.

Рисунок 3.2 – Условно-графическое обозначение КР580ВВ51А

Описание выводов и основные параметры микросхемы КР580ВВ51А представлены в таблицах 3.3 и 3.4 соответственно.

Таблица 3.3 – Назначение выводов микросхемы КР580ВВ51А

|

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

|

1, 2, 5 – 8, 27, 28 |

D2 - D7, D0, D1 |

Входы/ выходы |

Канал данных – обмен информацией между микропроцессором и микросхемой |

|

Продолжение таблицы 3.3 |

|||

|

3 |

RXD |

Вход |

Приемник микросхемы |

|

4 |

GND |

- |

Общий |

|

9 |

Вход |

Синхронизация передачи |

|

|

10 |

Вход |

Запись информации |

|

|

11 |

Вход |

Выбор микросхемы |

|

|

12 |

C/ |

Вход |

Управление/ данные |

|

13 |

Вход |

Чтение информации |

|

|

14 |

RXRDY |

Выход |

Готовность приемника |

|

15 |

TXRDY |

Выход |

Готовность передатчика |

|

16 |

SYNDET/ BD |

Вход/ Выход |

Двунаправленый трехстабильный программируемый вход/ выход |

|

17 |

Вход |

Готовность внешнего устройства принять данные |

|

|

18 |

TXEND |

Выход |

Конец передачи |

|

19 |

TXD |

Выход |

Передатчик микросхемы |

|

20 |

SYN |

Вход |

Синхронизация |

|

21 |

SR |

Вход |

Установка исходного состояния (общий сброс) |

|

22 |

* |

Вход |

Готовность внешнего устройства передать данные |

|

23 |

* |

Выход |

Запрос приемника внешнего устройства на прем данных |

|

24 |

* |

Выход |

Запрос передатчика внешнего устройства на передачу данных |

|

25 |

Вход |

Синхронизация приема |

|

|

26 |

VCC |

- |

Напряжение питания |

Таблица 3.4 – Основные электрические параметры КР580ВВ51А

|

Параметры |

Величина |

|

Номинальное напряжение питания |

5В ± 5% |

|

Выходное напряжение высокого уровня |

≥2,5 В |

|

Выходное напряжение низкого уровня |

≤0,4 В |

|

Ток потребления |

≤100 мА |

|

Ток утечки на входах |

≤|-1|мкА |

|

Выходной ток в состоянии «выключено» |

≤|-1|мкА |

|

Длительность сигналов WR, RD |

≥250 нс |

|

Время задержки сигналов D7…D0 относительно RD |

≤250 нс |

Микросхема может работать в двух режимах.

Синхронный режим характеризуется непрерывным потоком передаваемой/ принимаемой информации. Для установления синхронизации между передатчиком/ приемником микросхемы КР580ВВ51А и приемником/ передатчиком внешнего устройства и выделения из последовательного потока символов полезной информации в поток информации вводятся кодирующие слова (синхросимволы). Информационная (5-8 бит) и временная длины синхросимвола и слова равны.

Если между словами данных имеются временные промежутки, то они заполняются синхросимволами, которых может быть один или два (устанавливается программно). Если запрограммирован контроль данных по четности (нечетности), то после каждого слова данных вставляется бит контроля.

Сигналы на внешних входах микросхемы асинхронны по отношению к сигналу SYN. Однако соотношение частот общей синхронизации микросхемы (fSYN) и частот синхронизации передачи/ приема (fTXSYN, fRXSYN) должно быть:

fTXSYN <fSYN /30,

fRXSYN <fSUN /30.

При этом обеспечивается скорость передачи/ приема информации V = TX (RX) = 0-64 Кбод. Скорость численно равна частоте синхронизации передачи/ приема и определяется возможностями внешнего устройства.

Асинхронный режим характеризуется одиночными посылками информации, инициализация которых определяется либо микропроцессором системы (где стоит микросхема КР580ВВ51А), либо внешним устройством.

Асинхронный режим имеет три подрежима, отличающихся друг от друга различным соотношением численных значений частот синхронизации передачи/ приема к скорости передачи:

подрежим 1:1 соотношения частот общей синхронизации микросхемы и синхронизации передачи/ приема, а также скорости передачи аналогичны синхронному режиму;

подрежим 1:16:

VTX = (fTXSYN /64) = 0-9,6 Кбод;

VRX = (fRXSYN /64) = 0-9,6 Кбод;

подрежим 1:64:

VTX = (fTXSYN /16) = 0-19,2 Кбод;

VRX = (fRXSYN /16) = 0-19,2 Кбод;

В подрежимах 1:16 и 1:64 должны выполняться условия:

fTXSYN < fSYN /4,5;

fRXSYN < fSYN /4,5.

Программирование микросхемы на требуемый режим работы производится путем занесения в соответствующие регистры слов инструкций режима, синхросимволов (для синхронного режима) и команд. При передаче/ приеме информации микросхема устанавливается в исходное состояние сигналом SR. После записи инструкции режима, синхросимвола и инструкций команд она переходит в один из пяти основных режимов работы.

Рассмотрим режим работы микросхемы – асинхронная передача. Временные диаграммы для данного режима приведены на рисунке.

После записи в микросхему данных в параллельном формате происходит автоматическое присоединение к каждой посылке старт-бита и стоп-бита. Бит контроля четности (если он запрограммирован) вводится перед битами останова и может иметь нулевое или единичное значение.

Если в инструкции команды в разряд D0 записана 1 и на входе устанавливается напряжение низкого уровня, то информация в виде последовательного потока данных подается на вывод TхD с частотой, кратной 1:1, 1:16 или 1:64 части частоты синхронизации передатчика (как определено инструкцией режима). Если микросхема не содержит информацию для передачи, то на выходе TхD устанавливается напряжение высокого уровня. Если в инструкции команды запрограммирован режим «пауза», то на выходе TхD устанавливается напряжение низкого уровня.

Структурная схема микросхемы КР580ВВ51А приведена на рисунке 6.

Рисунок 3.3 – Структурная схема микросхемы КР580ВВ51А

3.3 Функциональная схема узла

Функциональная схема узла представлена на рисунке 3.3.

Рисунок 3.5 – Функциональная схема узла приемопередатчика с преобразователем сигнала ТТЛ

3.4 Описание работы узла

Работа блока определяется функционированием БИС УСАПП. Синхронный режим характеризуется непрерывным потоком передаваемой/ принимаемой информации. Асинхронный режим характеризуется одиночными посылками информации, инициализация которых определяется либо микропроцессором системы (где стоит микросхема КР580ВВ51А), либо внешним устройством.

Сигнал для передовой части поступает с выхода TxD УСАПП и передается в линию через оптрон и транзистор. Принимаемый из линии сигнал поступает на оптрон через схему повышения помехоустойчивости, выполненную на резисторах. Принятый из линии сигнал преобразуется в ТТЛ-уровень и поступает на выход УСАПП.

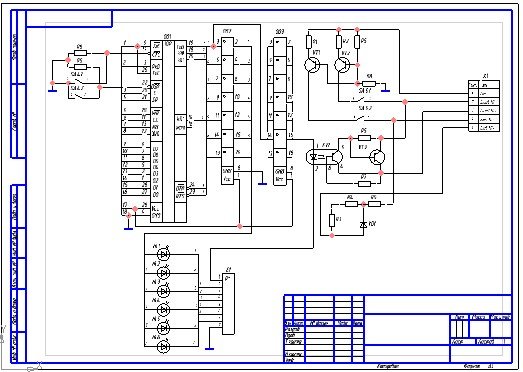

3.5 Описание принципиальной электрической схемы узла

Транзисторы VT1, VT2 работают как источники тока, величина которого определяется резисторами R1, R2, R3, R4. Переключатели SA1, SA2 позволяют образовать питание, соответственно, передающей и принимающей части блока.

Сигнал для передовой части поступает с выхода TxD УСАПП и передается в линию через онтрон EV1 и транзистор VT3.

Принимаемый из линии сигнал поступает на оптрон EV2через схему повышения помехоустойчивости, выполненную на резисторах R7, R8, R9. Принятый из линии сигнал с онтрона EV2 преобразуется в ТТЛ-уровень на резисторе R11 и поступает на выход УСАПП.

4 Расчет временных задержек в схеме функционального узла

Рассмотрим задержки в узле приемопередатчика с преобразователем сигнала ТТЛ в момент, когда работают все микросхемы входящие в узел. Данными для расчета мощности являются значения электрических параметров микросхем.

Время задержки для данного процесса будет рассчитываться по следующей формуле:

+ Т3,

где – время задержки микросхемы КР580ВВ51А; , Т3 – время задержки микросхемы К561ПУ4.

Подставляя значения, получим:

нс

5 Расчет мощности, потребляемой узлом от источника питания

Рассмотрим потребляемую узлом приемопередатчика с преобразователем сигнала ТТЛ мощность в момент, когда работают все микросхемы входящие в узел. Данными для расчета мощности являются значения электрических параметров микросхем, индикаторов и транзисторов.

Мощность, которую потребляет узел приемопередатчика с преобразователем сигнала ТТЛ, можно рассчитать по следующей формуле:

+ Р3+Р4+P5,

где Р – мощность, потребляемая узлом приемопередатчика с преобразователем сигнала ТТЛ; – мощность, потребляемая микросхемой КР580ВВ51А; , Р3 – мощность, потребляемая микросхемой К561ПУ4.

Определим мощности, потребляемые микросхемами КР580ВВ51А и К561ПУ4:

Р = U · I,

где Р – мощность, потребляемая регистром; U – напряжение питания; I – ток потребления.

Подставив значения, получим:

Р1 = 5 · 100 = 500 мВт и Р2 = 5 · 3 = 15 мВт

Тогда, общая мощность:

Р = 500 + 15 + 15 = 530 мВт ≈ 1 Вт

Выводы

В данной расчетно-графической работе мы исследовали модуль УМПК-80/МИ1 и рассмотрели приемопередатчика с блоком преобразователя сигнала ТТЛ.

В процессе работы были описаны все микросхемы, входящие в модуль УМПК-80/МИ1 и подробнее микросхемы, входящие в узел приемопередатчика с преобразователем сигнала ТТЛ

Также нами были произведены расчеты времени задержки и мощности узла приемопередатчика с блоком преобразователя сигнала ТТЛ исходя из параметров отдельных микросхем.

Список использованных источников

1 Интегральные микросхемы. Справочник (Б.В. Тарабрин, Л.Ф. Мунин, Ю.Н. Смирнов и др.,под. Ред. Тарабрина Б.В – М.: Радио и связь; 1984 – 528 с. ил.

2 Хвощ С.Т, и др Микропроцессоры и микроЭвм в системах автоматического управления: Справочник/ С.Т. Хвощ, Н.Н. Варлинский, Е.А. Попов; под общ. Ред С.Т. Хвоща. – Л.: Машиностроение. Ленингр. отд-ние, 1987. – 640 с.

3 Нефедов А.В. Интегральные микросхемы и их зарубежные аналоги. Справочник. Т2 – М.: ИП радиоСофт, 1999-640 с.:ил.

4 Микропроцессоры (в 3-х книгах) кн 1. Архитектруа и проектирование микроЭВМ. Организация вычислительных процессов. Под ред Преснухина Л.Н. М.: Высшая школа, 1986. – 495 с.: ил.

5 Микропроцессоры в 3-х книгах кн2. Средства сопряжения. Контролирующие и информационно управляющие системы. Под ред Преснухина Л.Н. М.: Высшая школа, 1986. – 383 с.: ил.

6 Микропроцессорные автоматические системы регулирования. Основы теории и элементы: Учеб. Пособие/В.В. Солодовников, В.Г. Коньков, В.А. Суханов, О.В. Шевяков. Под ред В.В. Солодовникова. – М.: Высшая школа, 1991 255 с.:ил.

7 Микропроцессоры и микропроцессорные комплекты интегральных микросхем Справочник в 2-х томах/ том 1 /Н.Н. Аверьянов, А.И. Березенко, Ю.И. Борщенко и др, под ред В.А.Шахнова М.: Радио и связь, 1988 – 368 с.:ил.

8 МикроЭВМ : в 8 кн.: Практ. пособие/ под.ред. Л.Н. Преснухина. Кн.7 Учебные стенды/ Ю.И. Волков, В.Л. Горбунов, Д.И.Панфилов, С.Г. Шаронин. – М.:Высш. шк., 1988. – 224 с.: ил.

9 Шило В.Л. Популярные цифровые микросхемы: Справочник 2-е изд.,испр – Челябинск: Металлургия, Челябинское отделение, 19889. – 352с:ил. – (Массовая радиобиблиотека вып.1111).

10 Новиков Ю.В. Основы цифровой схемотехники. Базовые элементы и схемы. Методы проектирования. – М.: Мир, 2001. – 379 с., ил. – (Современная схемотехника).

11 Стандарт предприятия: Общие требования и правила оформления выпускных квалификационных работ, курсовых проектов (работ), отчетов по РГР, по УИРС, по производственной практике и рефератов. – М.: 2000. – 62с.

12 ГОСТ 2.743-91 ЕСКД Обозначения условные графические в схемах. Элементы цифровой техники.

Приложение А

Схема электрическая принципиальная узла приемопередатчика

с преобразователем сигнала ТТЛ

Чертежи:

Скачать: